DOI: 10.1002/adem.((please add manuscript number))

# Robust free-standing nano-thin SiC membranes enable direct photolithography for MEMS sensing applications $^\dagger$

Hoang-Phuong Phan<sup>\* ‡</sup>, Tuan-Khoa Nguyen<sup>‡</sup>, Toan Dinh, Alan Iacopi, Leonie Hold, Muhammad J.A. Shiddiky, Dzung Viet Dao and Nam-Trung Nguyen

((Optional Dedication))

- [†] Dr. H.-P. Phan, Mr. T.-K. Nguyen, Dr. T. Dinh, Mr. A. Iacopi, Ms. L. Hold, Dr. M. J. A. Shiddiky, Dr. D.V. Dao, Prof. Dr. N.-T. Nguyen Queensland Micro and Nanotechnology Centre Griffith University, West Creek Road, Nathan, Qld 4111, Australia

- [\*] E-mail: hoangphuong.phan@griffithuni.edu.au

- [‡] H.-P. Phan and T.-K. Nguyen contributed equally to this work.

[\*\*] This work was performed in part at the Queensland node of the Australian National Fabrication Facility, a company established under the National Collaborative Research Infrastructure Strategy to provide nano and microfabrication facilities for Australia's researchers.

#### **Abstract**

This work presents fabrication of micro structures on sub-100 nm SiC membranes with a large aspect ratio up to 1:3200. Unlike conventional processes, our approach starts with Si wet etching to form suspended SiC membranes, followed by micro-machined processes to form free-standing microstructures such as cantilevers and micro bridges. This technique eliminates the sticking or the under-etching effects on free-standing structures, enhancing mechanical performance which is favorable for MEMS applications. In addition, post-Sietching photography also enables the formation of metal electrodes on free standing SiC membranes to develop electrically-measurable devices. To proof this concept, we demonstrated a SiC pressure sensor by applying lithography and plasma etching on released ultrathin SiC films. The sensors exhibit excellent linear response to the applied pressure, as well as good repeatability. The proposed approach opens a pathway for the development of self-sensing free-standing SiC sensors.

#### Introduction

Silicon carbide micro electromechanical systems (MEMS) has been an active research topic for more than a decade thanks to its superior properties such as large energy gap, chemical inertness, and large Young's modulus [1,2,3,4,5]. Silicon carbide finds applications in high power electronics (e.g. Schottky diode, transistors) and sensing devices including flame detection, gas sensing, thermal based sensors and pressure sensors [6,7,8,9]. In addition, owing to the corrosive tolerance and mechanical robustness, SiC has also been utilized as a coating layer to improve the wear resistance of devices and instruments [10,11]. Among more than 200 types of SiC crystals, cubic silicon carbide, which can be epitaxially grown on Si substrates, has attracted great attention. The different physical properties between SiC and Si such as thermal expansion, crystal lattice sizes, and different band gaps result in numerous interesting phenomena including large residual stress and the SiC/Si heterojunction [12,13,14]. In addition, the SiC on Si platform also enables the fabrication of SiC micro structures where the bottom Si layer can be removed with a relatively high etching rate of more than 10 µm/min in comparison to the low etching rate of bulk SiC wafer, which is typically several hundred nm/min [15,16].

Numerous free-standing SiC microstructures such as cantilevers, doubly clamped bridges, or micro-discs have been realized, where SiC films are initially patterned followed by a standard Si etching process to remove the substrate. A comprehensive review on the fabrication of SiC micro/nano structures can be found elsewhere [17]. A common method to remove the Si substrate is the use of Si wet-etching employing different etchants such as KOH, TMAH, or HNA [18,19,20,21]. In many cases, Si wet-etching is more preferable than dry-etching owing to its low cost, simple equipment, high etch-rate, excellent material selectivity, as well as the capability of processing multiple wafers simultaneously [22]. However, since the Si-etchants are relatively aggressive, the metallization to form electrodes for SiC devices is a challenging issue [23,24]. To date, most of the suspended SiC devices fabricated using Si-wet etching rely

on external sensing source such as Raman spectroscopy, and optical interferometer, while self-sensing devices utilizing electrical measurement have rarely been reported [25,26,27]. Additionally, wet etching applied to soft structures (e.g. cantilevers) could cause the sticking phenomenon or the under-etching effect, which adversely damages these MEMS devices [28]. In this work, we report the development of a fabrication technique compatible with Si wetetching to fabricate SiC MEMS devices with no effect on the subsequent metallization process. Unlike conventional approaches, our process starts with Si wet etching to form suspended SiC membranes, which is followed by other lithography steps to form freestanding microstructures such as cantilevers, and micro bridges. It should be pointed out that a similar technique has been reported in SiN membranes, with relatively small window sizes [29,30]. However, to the best of our knowledge, there has been no report on utilizing the direct lithography process into SiC nano membranes. In addition, application of lithography on large-scale suspended membranes with an aspect ratio of above 1:3000 is also unprecedented. The proposed process is feasible due to the robustness of the nanometer-thick SiC membranes, which allows photoresist spin-coating, as well as depositing and etching metal contact to be directly performed on the surface of suspended SiC areas. As proof of the concept for this method, we fabricated and demonstrated a SiC pressure sensor with a membrane thickness of 94nm, which can detect a large range of pressure up to 1.5 bar. The proposed process is also suitable for the development of other micro/nano structures such as cantilevers, and doubly clamped beams without substrate-sticking.

## **Principle of the fabrication process**

Silicon carbide was grown on 6-inch Si wafers in a hot wall chamber using the low pressure chemical vapor deposition process (LPCVD) at above  $1000^{\circ}$ C. Prior to the growth process, ptype Si (100) wafers with a concentration of  $10^{14}$ cm<sup>-3</sup> were cleaned using the RCA process. The detail of the growth process can be found elsewhere, in which silane (SiH<sub>4</sub>) and propylene (C<sub>3</sub>H<sub>6</sub>) server as precursors [15]. The thicknesses of SiC films are controllable, and

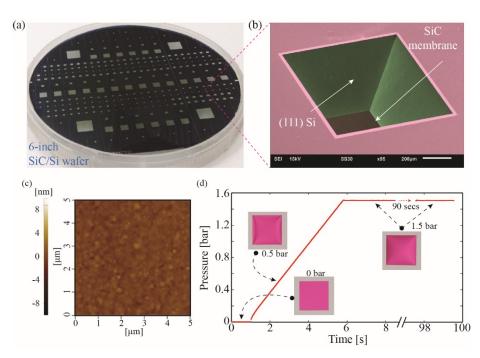

obtained by modifying the number of growth cycles. It should be noted that, our process deposited the SiC films on both sides of the starting Si wafers, where only the functioning layer on the top surface was smoothed prior to deposition. The SiC layer at the bottom was utilized as the etching mask for Si removal to simplify the requirement for the mask for the wet etching. Open windows for Si wet etching on the backside were created using inductive coupled plasma etching (ICP) in which HCl with a flow rate of 50 sccm at 4 mT was employed as the reactive gas. The etching rate of the ICP process was approximately 100nm/min. Subsequently, the exposed Si areas with a thickness of 400µm were removed in KOH at 80°C with an etching rate of approximately 1.4µm/min. Figure 1 (a) shows a photograph of a 6-inch SiC-on-Si wafer after patterning the Si substrate. The thickness of the films was 94 nm, which was measured using NANOMETRICS Nanospec/AFT 210. The thickness measurement was performed on several points on the 6-inch wafers, showing a uniformity of ±1%. The AFM image of the films showed a small roughness of below 2 nm in all films, as shown in Figure 1(b). No significant difference in the roughness was observed for the films with thicknesses varying from 94 nm to 200 nm.

Figure 1. (a) Arrays of SiC membranes fabricated from a 6 inch SiC-on-Si wafer. (b) SEM image of a SiC membrane with a thickness of 94nm. (c) An AFM image of 94nm SiC film showing a RMS roughness of below

2 nm; (d) The pressure test applied to the suspended membrane with dimension of  $94\text{nm} \times 300\mu\text{m} \times 300\mu\text{m}$ , showing its mechanical robustness, which can withstand high pressure up to 1.5 bar. (The aspect ratio between thickness and length of the membrane is approximately 1:3200)

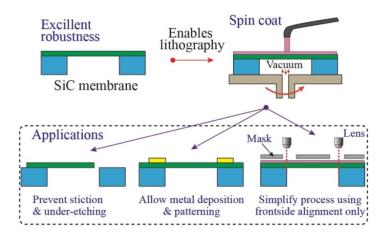

The 6-inch wafer was then diced into 10mm × 10mm chips. Figure 1(b) shows a typical SEM image taken from the back side of a 94nm × 300µm × 300µm SiC membrane. The bulging test was then performed to investigate the strength of the membrane with thickness varying from 94nm to 202nm. In the bulging test, the chips with free-standing SiC membranes were mounted on an enclosed chamber, in which pressure can be applied using an Elveflow<sup>TM</sup> OB1 Mk3 pressure controller. Figure 1(c) shows that the  $94\text{nm} \times 300\mu\text{m} \times 300\mu\text{m}$  membranes can withstand pressure levels above 1.5 bar. In addition, the high pressure levels (e.g., 1.5 bar) were maintained for several minutes, implying that there was no air leak through the membrane. The same phenomenon was also observed in membranes with larger thicknesses of 150nm and 202nm. Furthermore, the membranes were subjected to a negative pressure of -1bar with respect to the atmospheric pressure, showing no damage and leakage, indicating that our nano thin SiC membranes can withstand high vacuum levels. The excellent robustness allows the lithography process to be directly performed onto the free-standing SiC membrane, as (i) SiC/Si chips can be fixed on a vacuum chuck (with a vacuum level typically below 1 bar), and (ii) photoresist can be deposited, exposed, and developed without inducing any damage to the SiC membrane. This new approach offers several advantages over the conventional fabrication process, as illustrated in Figure 2. In particular, free-standing structures can be formed after a Si wet-etching step; therefore, problem regarding wet-stiction to the Si substrate can be avoided. Additionally, the formation of metal electrodes for SiC devices is also possible, since depositing and etching metals can be carried out after Si removal using aggressive chemicals such as KOH or TMAH. Furthermore, because SiC possesses excellent visible light transparency with a transmittance of above 65% for wavelengths varying from 450nm to 680nm [1], the wet-etched micro structures of the Si substrate can be observed through the SiC thin film. This enables the alignment of the top layers (e.g. metal electrodes or SiC functional elements) with the back side layer (Si). In other words, the robust sub 100nm SiC films with high aspect ratio of 3200 can eliminate the requirement for a double-side aligner to form SiC micro structures.

Figure 2. Concept of photolithography process of suspended nano thin SiC membranes.

### Demonstration of the lithography on suspended membrane

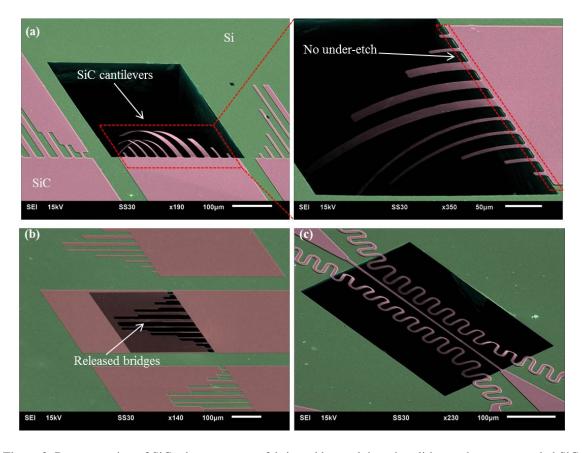

The following experiments were carried out to demonstrate the feasibility of the proposed process to form numerous SiC MEMS structures. Figure 3 shows photographs of SiC micro cantilevers, doubly clamped beams, and suspended spring shapes for micro heaters fabricated employing the direct photolithography on the free-standing SiC nano thin membrane. Initially, an AZ6612 photoresist layer with a thickness of 1.2µm was spin-coated, and then soft-baked at 100°C for 1 min. Next, the photoresist was exposed with a contact mode and then developed to transfer micro designs onto the SiC membrane. Subsequently, the top SiC layer was dry etched using ICP for approximately 2 mins. Finally, the photoresist was completely removed using oxygen plasma (see supplementary document). Due to the residual stress in SiC film, the free-standing cantilevers were significantly bent downward; nevertheless, no substrate-sticking was observed in the released structures, Figure 3(a). Additionally, the fixed end of the cantilevers can be well aligned with the edge of the opened Si windows underneath due to the transparency of SiC, Figure 3(b). This phenomenon solves the under-etch problem that frequently occurs during the fabrication of free-standing structures using wet etching,

which could degrade the performance of devices such as diminishing the resonant frequency or reducing the Q-factor due to the clamping loss [31]. It should be pointed out that, owing to the wide band gap of SiC, not only nanothin films, but SiC membranes with a large thickness of several tens micrometers are also transparent to visible wavelength. Therefore, our front-sided aligning method can be considered a standard technique for the fabrication of SiC films with a wide range of thicknesses. Furthermore, similar photolithography steps including metal-deposition and metal-wet-etching can be performed and repeated several times to build more functions or configurations, until the free-standing SiC area is patterned.

Figure 3. Demonstration of SiC micro structures fabricated by applying photolithography on suspended SiC membranes. (a) SiC cantilevers bending down after being released (no sticking was observed); (b) Doubly-clamped SiC beams; (c) Suspended spring structures for micro heater applications.

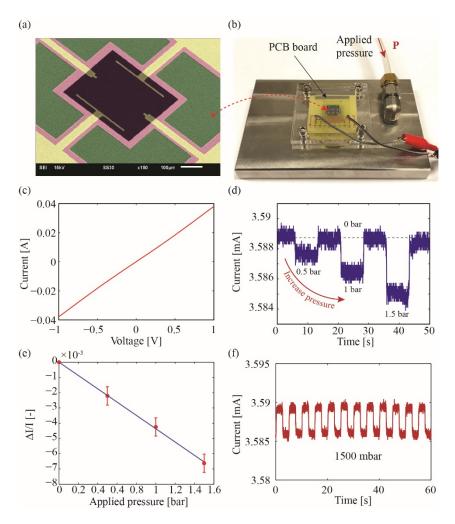

Figure 4(a) shows a self-sensing SiC membrane with metal electrodes and the SiC sensing configuration was fabricated following the wet etching of Si. A Ni film with a thickness of 200nm was deposited onto the SiC layer using sputtering. Next, the first photolithography

process was applied to the free-standing Ni/SiC membrane to pattern the electrodes. Subsequently, another lithography step combined with SiC dry etching was applied to define the SiC sensing structure (see supplementary document). The Ni electrodes were patterned on the free standing membrane to form a van der Pauw structure, enabling Hall measurement. Accordingly, the two parallel-line electrodes were employed to apply a constant current, while the two dot-shaped electrodes were used to measure the Hall voltage under an external magnetic field. Based on the Hall measurement, the SiC films were found to be an n-type semiconductor with a doping concentration of approximately  $10^{16} {\rm cm}^{-3}$ . For the characterization of the pressure sensors, only parallel-line electrodes were utilized to measure the resistance change of the membrane under applied pressures.

Figure 4. Demonstration of self-sensing SiC membranes. (a) SEM image of a SiC pressure sensor; (b) Experimental setup; (c) I-V curve of a SiC piezoresistor; (d) The response of output current versus different

applied pressure; (e) The linear relationship between relative current change and pressure; (f) Excellent repeatability of the sensors after testing cycles.

Demonstration of the self-sensing SiC membrane was performed using the experimental setup shown in Figure 4(b). The SiC chip was mounted and wire-bonded onto a PCB board, which was subsequently placed over an enclosed chamber, where pressures can be precisely generated using a controller. The principle of the self-sensing SiC membrane is based on the piezoresistive effect of the SiC film, which utilizes the change of the SiC resistance under mechanical impacts (e.g. force, pressure, stress)[30]. The piezoresistive effect in SiC has been widely utilized in SiC pressure sensors which were developed using a dry etching process [32-36]. A comprehensive review on the applications of the piezoresistance of SiC can be found in [37].

As show in Figure 4(c), the linear current voltage (I-V) characteristic of the 94-nm SiC membrane indicates the good Ohmic contact between Ni and SiC. Next, a constant voltage was applied to the SiC resistors, while the output current was monitored under applied pressure using Agilent B4105, Figure 4(d). The change in the current flowing through the SiC resistor was clearly observed under different pressures, and the current also returned to its original value, when the applied pressure was removed. Additionally, the output currents decreased linearly as applied pressures increased, which is a desired property for sensing applications, Figure 4(e). The current change in the SiC membrane also shows an excellent repeatability for numerous pressurizing cycles, Figure 4(f). Using the simple read-out configuration for self-sensing SiC membrane, the proposed platform enables the development of electrically-sensing devices, including cantilevers and resonators, which have rarely been reported.

#### **Conclusion**

This work presents a novel technique to fabricate SiC MEMS structures by applying the lithography process directly on robust free-standing SiC sub 100nm-thick membranes. Experimental results show the potential of this new method to fabricate a variety of devices such as cantilever and self-sensing membrane, where the sticking problem can be addressed and the conventional double-sided alignment can be completely replaced by single-sided alignment only. The developed photolithography process for robust membrane is not only suitable for a single chip, but also applicable for wafer-scale fabrication, making it an excellent solution for high throughput SiC based MEMS.

## Acknowledgement

This work was partially funded by the linkage grants LP150100153 and LP160101553 from the Australian Research Council (ARC). This work was performed in part at the Queensland node of the Australian National Fabrication Facility, a company established under the National Collaborative Research Infrastructure Strategy to provide nano and micro-fabrication facilities for Australia's researchers. H.-P. Phan acknowledge the Griffith University Postdoctoral Fellowship (GUPF).

### Reference

- [1] H.-P. Phan, H.H. Cheng, T. Dinh, B. Wood, T.-K. Nguyen, F. Mu, H. Kamble, R. Vadivelu, G. Walker, L. Hold, A. Iacopi, B. Haylock, D.V. Dao, M. Lobino, T. Suga, N.-T. Nguyen, ACS Appl. Mater. Interfaces. 2017, 9, 27365.

- [2] D. Nakamura, I. Gunjishima, S. Yamaguchi, T. Ito, A. Okamoto, H. Kondo, S. Onda, K. Takatori, *Nature* **2004**, *430*, 1009.

- [3] T.-K. Nguyen, H.-P. Phan, T. Dinh, J. Han, S. Dimitrijev, P. Tanner, A.R.M. Foisal, Y. Zhu, N.T. Nguyen, D.V. Dao, IEEE Electron Devic. Lett. **2017**, *38*, 955.

- [4] H.A. Moghadam, S. Dimitrijev, J. Han, D. Haasmann, A. Aminbeidokhti, IEEE Trans. Electron Dev. 2015, 62, 2670.

- [5] D. Leisen, R. Rusanov, F. Rohlfing, T. Fuchs, C. Eberl, H. Riesch-Oppermann, O. and Kraft, 2015, 86(5), 055104.

- [6] D. G Senesky, B. Jamshidi, K. B. Cheng, A. P. Pisano, *IEEE Sens. J.* **2009**, *9*, 1472.

- [7] T. Lehmann, J. Baier, A. Leineweber, A. Kienzle, J. Bill, Adv. Eng. Mater. 2015, 17, 1631.

- [8] C.R. Eddy, D.K. Gaskill, *Science* **2009**, *324*, 1398

- [9] T. Dinh, H.-P. Phan, A. Qamar, P. Woodfield, N.-T. Nguyen, D.V. Dao, J. Microelectromech. Syst. 2017, 1.

- [10] K.-H. Zuo, Y.-P. Zeng, D. Jiang, Adv. Eng. Mater. 2013, 15, 491.

- [11] M.A. Lantz, B. Gotsmann, P. Jaroenapibal, T.D. Jacobs, S.D. O'Connor, K. Sridharan, R.W. Carpick, *Adv. Func. Mater.* **2012**, 22, 1639.

- [12] A. Qamar, P. Tanner, D. Viet Dao, H.-P. Phan, T. Dinh, IEEE Electron Devic. Lett. 2014, 35, 1293.

- [13] D. V. Dao, H.-P. Phan, A. Qamar, T. Dinh, RSC Adv. 2016, 6, 21302.

- [14] H.-P. Phan, T. Dinh, T. Kozeki, T.-K. Nguyen, A. Qamar, T. Namazu, N.-T. Nguyen, D. V. Dao, Appl. Phys. Lett. 2016, 109, 123502.

- [15] L. Wang, S. Dimitrijev, J. Han, P. Tanner, A. Iacopi, L. Hold, J. Crystal Growth. 2011, 329(1), 67–70.

- [16] S.A. Kukushkin, A.V. Osipov, J. Appl. Phys. 2013, 113, 024909.

- [17] C. A. Zorman, R. J. Parro, Phys. stat. sol. (b) 2008, 245(7), 1404–1424.

- [18] G.S. Wood, B. Sviličić, E. Mastropaolo, R. Cheung, Micromachines, 2016, 7, 208.

- [19] H.-P. Phan, T.-K. Nguyen, T. Dinh, G. Ina, A.R. Kermany, A. Qamar, J. Han, T. Namazu, R. Maeda, D.V. Dao, N.-T. Nguyen, Appl. Phys. Lett., 2017, 110, 141906.

- [20] L.Q. Zhou, G. Colston, M.J. Pearce, R.G. Prince, M. Myronov, D.R. Leadley, O. Trushkevych, R.S. Edwards, Appl. Phys. Lett. 2017, 111, 011904.

- [21] E. Maeda, R. Kometani, Appl. Phys. Lett. 2017, 111, 013102.

- [22] C.A. Zorman, R.J. Parro, Phys. Status Solidi B 2008, 245, 1404.

- [23] O. Tabata, R. Asahi, H. Funabashi, K. Shimaoka, S. Sugiyama, Sens. Actuators A 1992, 34, 51.

- [24] N. Fujitsuka, K. Hamaguchi, H. Funabashi, E. Kawasaki, T. Fukuda, Sens. Actuators A 2004, 114, 510.

- [25] G. Colston, S.D. Rhead, V.A. Shah, O.J. Newell, I.P. Dolbnya, D.R. Leadley, M. Myronov, *Mater. Design* **2016**, *103*, 244.

- [26] H. Jia, X. Wu, H. Tang, Z.R. Lu, P.X.L. Feng, In Proc. IEEE MEMS, 2015, 698.

- [27] J. Trevino, X.A. Fu, M. Mehregany, C.A. Zorman, J. Micromech. Microeng. 2014, 24, 065001.

- [28] K. Kim, T. Rim, C. Park, D. Kim, M. Meyyappan, J.S. Lee, Nanotechnology 2014, 25, 345501.

- [29] Turkmen, M., Aksu, S., Çetin, A. E., Yanik, A. A., and H. Altug, 2011, 19(8), 7921-7928.

- [30] C. Escobedo, Lab on a Chip, 2013, 13(13), 2445-2463.

- [31] D.T. Nguyen, W. Hease, C. Baker, E. Gil-Santos, P. Senellart, A. Lemaître, S. Ducci, G. Leo, I. Favero, *New J. Phys* **2015**, *17*, 023016.

- [32] A. Qamar, H.P. Phan, J. Han, P. Tanner, T. Dinh, L. Wang, S. Dimitrijev, D.V. Dao, J. Mater. Chem. C 2015, 3, 8804.

- [33] C.-H. Wu, C. A. Zorman, and M. Mehregany, IEEE Sensors J. 2006, 6(2), pp. 316–324.

- [34] M. Eickhoff and M. Stutzmann, J. Appl. Phys. 2004, 96(5), 2878.

- [35] R. S. Okojie, D. Lukco, V. Nguyen, and E. Savrun, IEEE Electron Device Lett. 2015, 36(2), 174-176.

- [36] N. Behnel, T. Fuchs, and H. Seidel, Int. Conf. Solid-State Sensors, Actuators & Microsystems, USA, 2009,

- [37] H.-P. Phan, D. V. Dao, K. Nakamura, S. Dimitrijev, and N.-T. Nguyen, J. Microelectromech. Syst. 2015, 24(6), 1663-1677.